| Case 8:                                         | 16-cv-00600-SJO-FFM Document 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9 Filed 07/11/16                                                       | Page 1 of 40 | Page ID #:114 |  |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------|---------------|--|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | BRANDON C. FERNALD (SB)<br>FERNALD LAW GROUP<br>510 West Sixth Street, Suite 700<br>Los Angeles, California 90014<br>Telephone: 323-410-0320<br>Facsimile: 323-410-0330<br>Email: brandon.fernald@fernal@<br>DAVID A. SKEELS (admitted J<br>DECKER CAMMACK ( admitt<br>WHITAKER CHALK SWINDI<br>301 Commerce Street, Suite 350<br>Fort Worth, Texas 76102<br>Telephone: (817) 878-0573<br>Facsimile: (817) 878-0573<br>Facsimile: (817) 878-0501<br>Email: dskeels@whitakerchalk<br>Attorneys for Plaintiff<br>NORTH STAR INNOVATION | dlawgroup.com<br>Pro Hac Vice)<br>ed Pro Hac Vice<br>LE & SCHWART<br>0 | )<br>Z PLLC  |               |  |

| 11                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |              |               |  |

| 12                                              | UNITED STATES DISTRICT COURT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                        |              |               |  |

| 13                                              | CENTRAL DISTRICT OF CALIFORNIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                        |              |               |  |

| 14                                              | NORTH STAR INNOVATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        |              | 600-SJO-FFM   |  |

| 15                                              | INC.,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        | 0.8.10-07-00 | 000-530-11141 |  |

| 16                                              | Plaintiff,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FIDST                                                                  | A MENIDED (  | COMPLAINT     |  |

| 17                                              | VS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FIRST A                                                                | AMENDED      | JUNIFLAINT    |  |

| 18                                              | ELITE SEMICONDUCTOR<br>MEMORY TECHNOLOGY INC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                        | RIAL DEMA    | NDED          |  |

| 19                                              | d/b/a ESMT, and KAGA<br>ELECTRONICS (USA) INC. d/t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                        |              |               |  |

| 20                                              | TAXAN,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <i>)/ a</i>                                                            |              |               |  |

| 21                                              | Defendants.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                        |              |               |  |

| 22                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ]                                                                      |              |               |  |

| 23                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |              |               |  |

| 24                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |              |               |  |

| 25                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |              |               |  |

| 26                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |              |               |  |

| 27                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |              |               |  |

| 28                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |              |               |  |

| +                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |              |               |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |              |               |  |

Plaintiff North Star Innovations Inc. ("Plaintiff" or "North Star"), by and through its attorneys, files this First Amended Complaint for Patent Infringement against Defendant Elite Semiconductor Memory Technology Inc. d/b/a ESMT ("ESMT") and Defendant Kaga Electronics (USA) Inc. d/b/a TAXAN ("Kaga"), and alleges as follows:

### **PARTIES**

North Star is a corporation organized and existing under the laws of the

State of Delaware, with a principal place of business at 600 Anton Blvd., Costa

Mesa, California 92626.

North Star is the owner of seminal patents in the fields of integrated

circuits, semiconductor memory architecture, and semiconductor memory devices,

including patents that address volatile memory, such as DRAM and SRAM.

Plaintiff's portfolio includes patents that teach valuable innovations and

improvements related to – among other things – speed, power consumption,

density, reliability, and cost. Plaintiff is actively engaged in licensing efforts with

respect to such technologies.

17 On information and belief, Defendant ESMT is a Taiwanese 3. 18 corporation organized and existing under the laws of Taiwan, with a principal place 19 of business at: Elite Technology Building, No.23, Industry East Rd. IV Science-20 Based Industrial Park, Hsinchu 300, Taiwan. Upon information and belief, ESMT 21 may be served with process in Taiwan as follows: by way of letters rogatory; 22 pursuant to the foreign country's laws governing domestic service of process, i.e., 23 through service by the clerk of Taiwan's court; or, with ESMT's consent, through 24 service upon ESMT's U.S. counsel, Dr. Christian E. Mammen, Hogan Lovells, 3 25 Embarcadero Center, Suite 1500, San Francisco, CA 94111, U.S.A.

4. According to the websites of ESMT and Kaga, ESMT is a provider of

various memory ICs. In contrast to main memory products, such as DRAM used

for PCs, servers, and workstations, ESMT focuses its design and manufacturing

-1 -

6

1

2

3

4

5

1 efforts on specialty legacy memory ICs, including DRAM products for such 2 markets as PC peripherals, IA products, consumer products, optical devices, and 3 communication devices. ESMT markets a full range of densities, from 1MB to 256MB, and a wide variety of specialty DRAM products, including EDO, SDRAM, 4 5 and DDR. On information and belief, ESMT, through its own website and through U.S. suppliers and distributors of electronic components such as Kaga, markets or 6 7 has marketed its products throughout the U.S. For example, at the time of the filing of the Original Complaint, Kaga's website stated: "KAGA and ESMT want to be 8 9 your specialty memory partner."

- 10 5. Kaga is a corporation organized and existing under the law of the State 11 of California, with its principal place of business at 780 Montague Expressway 12 Suite #403, San Jose, CA 95131-1318. Kaga may be served by serving its registered agent for services of process, Jeffrey Joseph Demello, 780 Montague Expressway 13 Suite #403, San Jose, CA 95131-1318. Alternatively, Kaga may be served by 14 serving its counsel of record, John F. Ward, at: Kelly Drye & Warren LLP, Attn: 15 John F. Ward, Esq., 16 101 Park Ave., New York, NY 10178, or at: 17 jward@kelleydrye.com.

- 18 6. According to its website, Kaga, a wholly-owned subsidiary of Japan-19 based Kaga Electronics Co., Ltd., is and/or was a distributor of electronic 20 components, including semiconductors and memory products. According to its 21 website, Kaga serves and/or served U.S. customers in various markets, including 22 "consumer electronics, industrial automation, automotive, medical equipment, 23 network/telecom, semi-infrastructural area, and gaming/amusement," and it functions as a sales agency for PC ... peripherals made by [various] worldwide 24 25 brands," including, at least as of the time the Original Complaint was filed, ESMT 26 products. At the time the Original Complaint was filed, Kaga's website specifically advertised that "KAGA and ESMT want to be your specialty memory partner." 27

- 28

## JURISDICTION AND VENUE

- 2 -

7. This action arises under the patent laws of the United States, 35 U.S.C. § 1 et seq., including §§ 271, 281, 282, 283, 284, and 285. This Court has subject matter jurisdiction over this patent infringement action pursuant to 28 U.S.C. §§ 1331, and 1338(a).

5 8. This Court has personal jurisdiction over ESMT. Upon information and belief, ESMT, directly or indirectly through its agents or suppliers, has regularly 6 7 conducted and continues to conduct business in the U.S., in the State of California, and in this judicial district. Further, upon information and belief, ESMT has, through 8 its actions, purposely availed itself of this forum, and such actions give rise to the 9 claims described in this Complaint, such that this Court's exercise of jurisdiction 10 would be reasonable and fair. On information and belief, Defendant, directly or 11 indirectly through its current and/or former suppliers or agents (such as, for 12 example, Kaga), has committed infringing activities in this judicial district by using, 13 14 marketing, offering for sale, selling, and/or importing products and systems that infringe the Patents-In-Suit (as defined below) or by placing such infringing 15 16 products and systems into the stream of commerce with the awareness, knowledge, 17 and intent that they would be used, offered for sale, or sold by others in this judicial 18 district and/or purchased by consumers in this judicial district.

19

1

2

3

4

9. This Court has personal jurisdiction over Kaga. Upon information and belief, Kaga has regularly conducted and continues to conduct business in the U.S., 20 21 in the State of California, and in this judicial district. On information and belief, Kaga has committed infringing activities in California and in this judicial district by 22 using, marketing, offering for sale, selling, and/or importing products and systems 23 that infringe the Patents-In-Suit (as defined below) or by placing such infringing 24 25 products and systems into the stream of commerce with the awareness, knowledge, 26 and intent that they would be used, offered for sale, or sold by others in this judicial 27 district and/or purchased by consumers in this judicial district. Further, this Court 28 has personal jurisdiction over Kaga because Kaga is incorporated under the laws of - 3 -

the State of California. Kaga has thereby availed itself of the privileges of 1 2 conducting business in the State of California and has sought protection and benefit from the laws of the State of California. This Court's exercise of personal 3 jurisdiction over Kaga would therefore comport with due process. 4 5 10. Venue is proper pursuant to 28 U.S.C. §§ 1391(b) and 1400(b). THE PATENTS-IN-SUIT 6 7 On February 23, 1999, U.S. Patent No. 5,875,143 ("the '143 Patent") – 11. entitled "Dynamic Memory Device with Refresh Circuit and Refresh Method" -8 9 was lawfully and properly issued by the United States Patent and Trademark Office ("USPTO"), after a full and fair examination. The named inventor on the '143 10 11 Patent is Jacob Ben-Svi of Austin, Texas. A true and correct copy of the '143 Patent 12 is attached hereto as Exhibit A and incorporated by reference. 13 12. Generally speaking, the '143 Patent teaches, among other things, an 14 optimized, flexible, programmable refresh circuit that reduces size and power 15 consumption in a DRAM or SDRAM memory device by allowing for partial refresh 16 of a memory array. 17 13. On October 3, 2000, U.S. Patent No. 6,127,875 ("the '875 Patent") – 18 entitled "Complimentary Double Pumping Voltage Boost Converter" - was 19 lawfully and properly issued by the United States Patent and Trademark Office 20 ("USPTO"), after a full and fair examination. The named inventors on the '875 21 Patent are Steven Peter Allen, Ahmad H. Atriss, Gerald Lee Walcott, and Walter C. Seelbach, all of Arizona. A true and correct copy of the '875 Patent is attached 22 hereto as Exhibit B and incorporated by reference. 23 24 14. Generally speaking, the '875 Patent teaches, among other things, an 25 efficient and compact voltage boosting circuit that boosts the available supply 26 voltage and limits output distortion. 27 On July 12, 2005, U.S. Patent No. 6,917,555 ("the '555 Patent") – 15. entitled "Integrated Circuit Power Management for Reducing Leakage Current in 28 - 4 -

Circuit Arrays and Method Therefor" – was lawfully and properly issued by the

United States Patent and Trademark Office ("USPTO"), after a full and fair

examination. The named inventors on the '555 Patent are Ryan D. Bedwell,

Christopher K.Y. Chun, Qadeer A. Qureshi, and John J. Vaglica, all of Texas. A

true and correct copy of the '555 Patent is attached hereto as <u>Exhibit C</u> and

incorporated by reference.

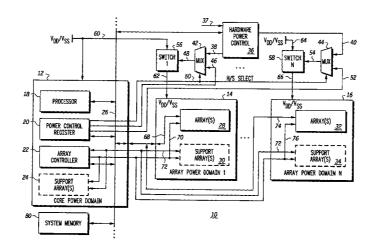

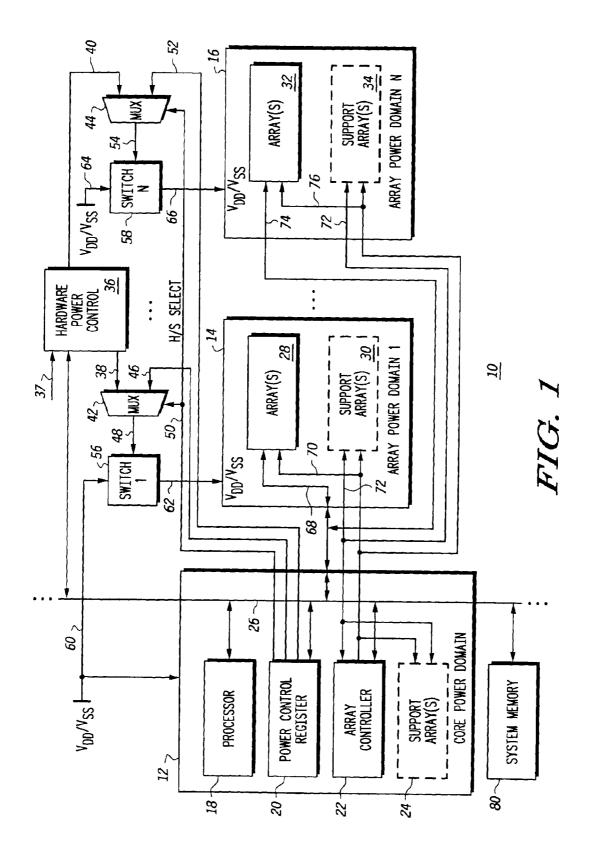

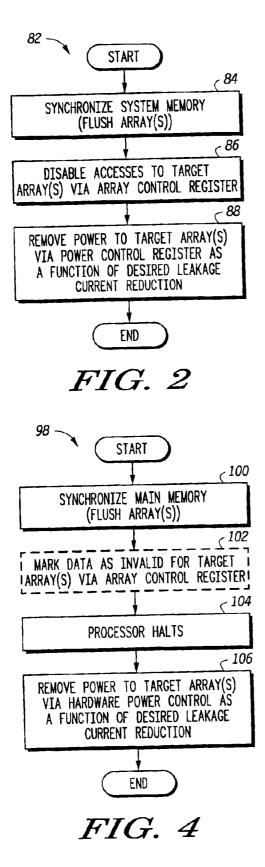

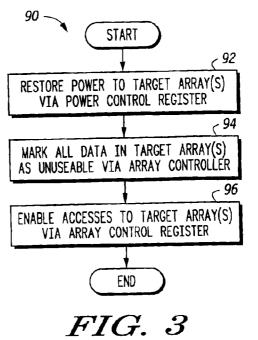

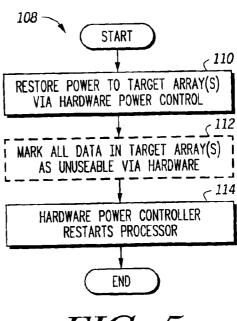

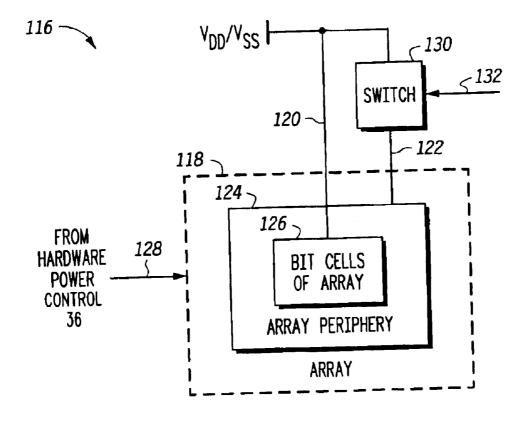

7 16. Generally speaking, the '555 Patent teaches, among other things, a

8 novel design for an integrated circuit with power management capabilities, where,

9 in certain embodiments, multiple, independent power planes are used to eliminate

10 or reduce leakage current.

11 17. The '143 Patent, the '875 Patent, and the '555 Patent may be referred

12 to individually as a "Patent-in-Suit" or collectively as the "Patents-in-Suit."

13 18. By way of assignment, Plaintiff is the owner of all right, title, and

14 interest in and to the Patents-in-Suit, including the rights to prosecute this action

15 and to collect and receive damages for all past, present, and future infringements.

- 16

- 17

18

19

20

21

22

23

24

25

26

27

## **COUNT ONE: INFRINGEMENT OF THE '143 PATENT**

19. Plaintiff incorporates the above allegations as if set forth here in full.

20. The '143 Patent is valid and enforceable. Defendants do not have a license to practice the patented inventions of the '143 Patent.

21. Defendants, individually or through their agents or suppliers, have infringed and are currently infringing, either literally or under the doctrine of equivalents, the '143 Patent by, among other things, making, using, offering for sale, selling, and/or importing within this judicial district and elsewhere in the United States – without license or authority – products, devices, or systems falling within the scope of one or more claims of the '143 Patent. For example, ESMT's 256Mb Mobile DDR SDRAM, ESMT Part Number M53D256328A ("ESMT's Mobile DDR SDRAM"), which, by way of example and upon information and

28

belief, is and/or has been imported, offered for sale, and/or sold by Kaga, directly infringes at least Claim 2 of the '143 Patent, either literally or under the doctrine of equivalents.

4

5

6

7

8

9

10

11

3

1

2

22. More specifically, ESMT's Mobile DDR SDRAM infringes at least Claim 2 because it meets each and every limitation of Claim 2, either literally or under the doctrine of equivalents. For example, the referenced product includes, among other things, "a reference register for storing a reference address and control logic coupled to said reference register, to said address generator, and to said decoder, wherein said control logic uses said addresses generated by said address generator and said reference address to determine which storage elements are in said first sub-set and which storage elements are in said second sub-set."

12 23. On information and belief, additional, similar models of ESMT's

13 memory products are believed to infringe one or more claims of the '143 Patent.

14 Plaintiff expressly reserves the right to assert additional claims and to identify

15 additional infringing products in accordance with the Court's scheduling order and

16 local rules.

17 24. Plaintiff has been damaged by Defendants' infringing conduct and will 18 continue to be damaged unless Defendants are enjoined from further infringement. 19 Accordingly, upon finding for Plaintiff, the Court should award to Plaintiff 20 damages adequate to compensate for the infringement, in an amount to be 21 determined at trial, but in no event less than a reasonable royalty for the use made 22 of the invention by the infringers, together with interest and costs as fixed by the Court. Further, upon judgment in favor of Plaintiff, the Court should permanently 23 24 enjoin Defendants from committing the infringing acts.

- 25

- 26

27

28

## **COUNT TWO: INFRINGEMENT OF THE '875 PATENT**

25. Plaintiff incorporates the above allegations as if set forth here in full.

26. The '875 Patent is valid and enforceable. Defendants do not have a license to practice the patented inventions of the '875 Patent.

2

3

4

5

7

27. Defendants have infringed and are currently infringing the '875 Patent by, among other things, making, using, offering for sale, selling, and/or importing within this judicial district and elsewhere in the United States – without license or authority - products, devices, and/or systems falling within the scope of one or more claims of the '875 Patent. For example, ESMT's 128 Mb DDR SDRAM, ESMT Part Number M13S128168A-5T ("ESMT's DDR SDRAM"), which, by 6 way of example and upon information and belief, is and/or has been imported, 8 offered for sale, and/or sold by Kaga, directly infringes at least Claim 1 of the '875 Patent, either literally or under the doctrine of equivalents. 9

10 28. More specifically, the referenced product infringes at least Claim 1 11 because it meets each and every limitation of Claim 1, either literally or under the doctrine of equivalents. For example, the referenced product includes, among other 12 things, a boost circuit that includes "a first switch coupled between the input 13 14 terminal and the output terminal and operated by a first phase signal; a second switch coupled between the input terminal and the output terminal and operated by 15 16 a second phase signal that is opposite to the first phase signal; a first capacitor 17 having a first terminal coupled to the output terminal and a second terminal coupled 18 for receiving a boost signal; and a second capacitor having a first terminal coupled 19 to the output terminal and a second terminal coupled for receiving the boost signal."

20 On information and belief, additional, similar models of ESMT's 29. 21 memory products are believed to infringe one or more claims of the '875 Patent. 22 Plaintiff expressly reserves the right to assert additional claims and to identify additional infringing products in accordance with the Court's scheduling order and 23 24 local rules.

25 30. Plaintiff has been damaged by Defendants' infringing conduct and will 26 continue to be damaged unless Defendants are enjoined from further infringement. 27 Accordingly, upon finding for Plaintiff, the Court should award to Plaintiff 28 damages adequate to compensate for the infringement, in an amount to be - 7 -

determined at trial, but in no event less than a reasonable royalty for the use made

of the invention by the infringers, together with interest and costs as fixed by the

Court. Further, upon judgment in favor of Plaintiff, the Court should permanently

enjoin Defendants from committing the infringing acts.

5

6

7

8

## **COUNT THREE: INFRINGEMENT OF THE '555 PATENT**

31. Plaintiff incorporates the above allegations as if set forth here in full.

32. The '555 Patent is valid and enforceable. Defendants do not have a license to practice the patented inventions of the '555 Patent.

Defendants have infringed and are currently infringing the '555 Patent 9 33. by, among other things, making, using, offering for sale, selling, and/or importing 10 11 within this judicial district and elsewhere in the United States - without license or 12 authority – products, devices, and/or systems falling within the scope of one or more claims of the '555 Patent. For example, ESMT's DDR SDRAM, which, by 13 way of example and upon information and belief, is and/or has been imported, 14 offered for sale, and/or sold by Kaga, directly infringes at least Claim 15 of the '555 15 16 Patent, either literally or under the doctrine of equivalents.

More specifically, the referenced product infringes at least Claim 15 17 34. because it meets each and every limitation of Claim 15, either literally or under the 18 doctrine of equivalents. For example, the above-referenced accused product is: "An 19 20 integrated circuit having power management comprising:<sup>1</sup> processing circuitry for 21 executing instructions; a plurality of memory bit cells contained within a memory 22 array, the plurality of memory bit cells being coupled to a power supply terminal 23 for creating a first power plane; memory array peripheral circuitry that is peripheral to the plurality of memory bit cells, the memory array peripheral circuitry being 24 25 selectively coupled to the power supply terminal for creating a second power plane 26 that is independent of the first power plane; and control circuitry coupled to the

27

28

<sup>&</sup>lt;sup>1</sup> Plaintiff does not hereby suggest or concede that the preamble of this or any other asserted claim constitutes a substantive limitation. That issue is expressly reserved for the claim construction stage.

memory array peripheral circuitry that is peripheral to the plurality of memory bit

cells, the control circuitry selectively removing electrical connectivity to the power

supply terminal of the memory array peripheral circuitry that is peripheral to the

plurality of memory bit cells."

5

6

7

8

9

35. On information and belief, additional, similar models of ESMT's memory products are believed to infringe one or more claims of the '555 Patent. Plaintiff expressly reserves the right to assert additional claims and to identify additional infringing products in accordance with the Court's scheduling order and local rules.

Plaintiff has been damaged by Defendants' infringing conduct and will 10 36. 11 continue to be damaged unless Defendants are enjoined from further infringement. 12 Accordingly, upon finding for Plaintiff, the Court should award to Plaintiff 13 damages adequate to compensate for the infringement, in an amount to be 14 determined at trial, but in no event less than a reasonable royalty for the use made 15 of the invention by the infringers, together with interest and costs as fixed by the 16 Court. Further, upon judgment in favor of Plaintiff, the Court should permanently enjoin Defendants from committing the infringing acts. 17

## **PRAYER FOR RELIEF**

WHEREFORE, Plaintiff respectfully prays for entry of judgment as follows:1. That Defendants have directly infringed, either literally or under the doctrine of equivalents, one or more claims of each of the Patents-In-Suit;

22 2. That Plaintiff is entitled to, and should recover, all damages to which

23 Plaintiff is entitled under 35 U.S.C. § 284, but in no event less than a reasonable

24 royalty;

25

18

19

20

21

3. That Defendants be ordered to provide an accounting;

4. That Plaintiff, as the prevailing party, shall recover from Defendants all

taxable costs of court;

28

| 1  | 5. That Plaintiff shall recover from Defendants all pre- and post-judgment                                              |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------|--|--|

| 2  | interest on the damages award, calculated at the highest interest rates allowed by                                      |  |  |

| 3  | law;                                                                                                                    |  |  |

| 4  | 6. That Plaintiff is entitled to enhanced damages from ESMT of up to                                                    |  |  |

| 5  | three times the amount found by the jury or ordered by the Court, pursuant to 35                                        |  |  |

| 6  | U.S.C. § 284;                                                                                                           |  |  |

| 7  | 7. That this case is exceptional and that Plaintiff therefore shall recover                                             |  |  |

| 8  | its attorney's fees and other recoverable expenses, under 35 U.S.C. § 285; and                                          |  |  |

| 9  | 8. That Plaintiff shall recover from Defendants such other and further                                                  |  |  |

| 10 | relief as the Court may deem appropriate.                                                                               |  |  |

| 11 | Dated: July 11, 2016                                                                                                    |  |  |

| 12 | /s/ Brandon C. Fernald<br>BRANDON C. FERNALD                                                                            |  |  |

| 13 | FERNALD LAW GROUP                                                                                                       |  |  |

| 14 | 510 West Sixth Street, Suite 700<br>Los Angeles, California 90014<br>Telephone: 323-410-0320<br>Facsimile: 323-410-0330 |  |  |

| 15 | Facsimile: 323-410-0320<br>Email: <u>brandon.fernald@fernaldlawgroup.com</u>                                            |  |  |

| 16 |                                                                                                                         |  |  |

| 17 | DAVID A. SKEELS (admitted <i>Pro Hac Vice</i> )<br>DECKER CAMMACK (admitted <i>Pro Hac Vice</i> )                       |  |  |

| 18 | WHITAKER CHALK SWINDLE &<br>SCHWARTZ PLLC                                                                               |  |  |

| 19 | 301 Commerce Street, Suite 3500<br>Fort Worth, Texas 76102                                                              |  |  |

| 20 | Telephone: (817) 878-0573<br>Facsimile: (817) 878-0501                                                                  |  |  |

| 21 | Email: <u>dskeels@whitakerchalk.com</u>                                                                                 |  |  |

| 22 | Attorneys for Plaintiff<br>NORTH STAR INNOVATIONS INC.                                                                  |  |  |

| 23 |                                                                                                                         |  |  |

| 24 |                                                                                                                         |  |  |

| 25 |                                                                                                                         |  |  |

| 26 |                                                                                                                         |  |  |

| 27 |                                                                                                                         |  |  |

| 28 | - 10 -                                                                                                                  |  |  |

# **EXHIBIT** A

## United States Patent [19]

Ben-Zvi

#### [54] DYNAMIC MEMORY DEVICE WITH REFRESH CIRCUIT AND REFRESH METHOD

- [75] Inventor: Jacob Ben-Zvi, Austin, Tex.

- [73] Assignee: Motorola, Inc., Schaumburg, Ill.

- [21] Appl. No.: 976,835

- [22] Filed: Nov. 24, 1997

#### **Related U.S. Application Data**

- [63] Continuation of Ser. No. 683,642, Jul. 15, 1996, abandoned.

- [51] Int. Cl.<sup>6</sup> ...... G11C 7/00

- [52] U.S. Cl. ...... 365/222; 365/185.11; 365/185.22;

- 365/230.03

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

4,914,630 4/1990 Fujisthima et al. ...... 365/222

5,247,655 9/1993 Khan et al. ..... 395/550

5,875,143

Feb. 23, 1999

FOREIGN PATENT DOCUMENTS

| 0488593 | 6/1992 | European Pat. Off |

|---------|--------|-------------------|

| 0609577 | 8/1994 | European Pat. Off |

**Patent Number:**

**Date of Patent:**

Primary Examiner—David Nelms Assistant Examiner—Hoai V. Ho

[11]

[45]

#### [57] ABSTRACT

A refresh circuit (230) and a method for the refresh of dynamic memory devices (201) are described where the rows to be refreshed are determined by a logical function and by a reference address (223). The availability of refresh signals (215) for the rows at the outputs (217) of a decoder (214) is determined by control logic (224) which is connected to an address generator (212) and to a reference register (222) which contains a reference address (223). By supplying the reference address (223) to the refresh circuit (230) it is possible to determine which rows are to be refreshed. The memory array (210) of the dynamic memory device (201) can be refreshed partially and energy consumption for the refresh can be reduced.

#### 13 Claims, 2 Drawing Sheets

Sheet 1 of 2

FIG. 1 -PRIOR ART-

Sheet 2 of 2

5,875,143

10

15

20

25

40

65

#### DYNAMIC MEMORY DEVICE WITH **REFRESH CIRCUIT AND REFRESH** METHOD

This application is a continuation of prior patent appli-5 cation Ser. No. 08/683,642 filed Jul. 15, 1996 now abandoned.

#### FIELD OF THE INVENTION

The present invention relates to a dynamic memory device, and a method to refresh dynamic memory devices, as for example but not limited to a Dynamic Random Access Memory (DRAM).

#### BACKGROUND OF THE INVENTION

Dynamic memory devices such as DRAM need to be refreshed. This consumes energy. In many systems energy consumption is very crucial for performance, and the power used for refreshing should be reduced.

Energy consumption can be reduced by using a memory that consists not only of a DRAM but also of a less power consuming static memory (SRAM). During standby mode critical data can be stored in the SRAM, and the DRAM can be switched off and not refreshed. Providing an SRAM leads to additional cost and space. Moreover, two different memory access cycles are required.

U.S. Pat. No. 5,331,601 describes a memory device that alters the input refresh addresses to access fewer memory cells to save power, or to address more memory cells to 30 decrease the refresh time. The circuit contains a simple transistor configuration that blocks certain address bits, then substitutes active bits in their place to the address decoder. The circuit also includes a controller that is responsive to the memory device entering the refresh mode. When the device 35 is used in refresh mode, the address bits may be passed unblocked to the address decoder for full user control.

Another prior art reference, European patent application 488 593, relates to the stability of the refresh in case the power supply fails.

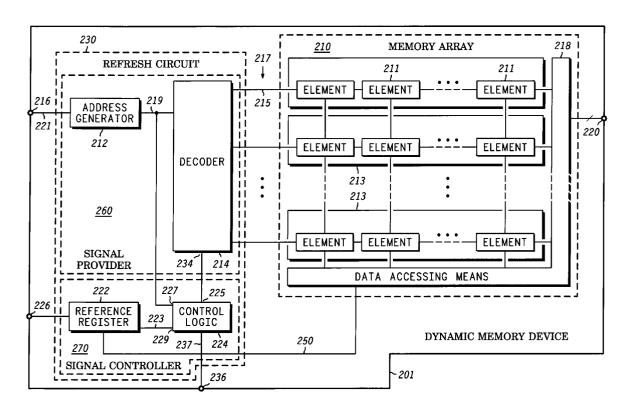

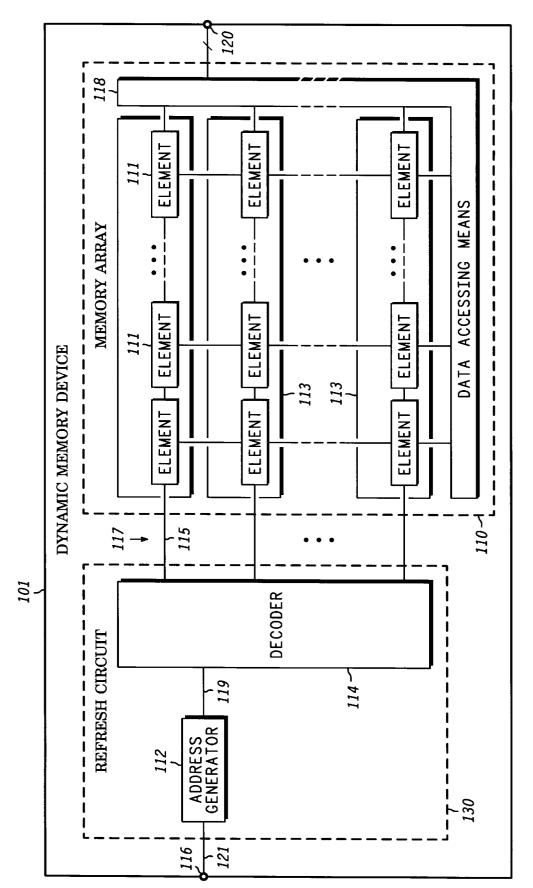

FIG. 1 shows a schematic block diagram of prior art dynamic memory device 101.

Dynamic memory device 101 comprises memory array 110, address generator 112 and decoder 114. The combination of address generator 112 and decoder 114 is referred to as refresh circuit 130. As shown in FIG. 1, dynamic memory device 101 also comprises data terminal 120 and optional terminal 116. Memory array 110 comprises a multitude of storage elements 111 and data accessing means 118. Data accessing means 118 is provided to write, read and update data which is stored in storage elements 111. Data accessing means 118 is connected to storage elements 111 and to data terminal 120.

Aphysical group of storage elements 111 in memory array 55 110 is referred to as block 113. Blocks 113 are logically designated by  $A_1, A_i \dots A_n$ . In memory array 110, the number of blocks 113 is n. Block addresses  $a_1, a_1, \ldots, a_n$  are logically assigned to blocks  $A_1, A_i \dots A_n$ . There is one block address a, for one block A,.

Outputs 117 of decoder 114 are connected to storage elements 111 of corresponding blocks 113. Address generator 112 is connected to decoder 114 and generates block addresses 119  $(a_1, a_i \dots a_n)$  corresponding to blocks 113  $(A_1, A_2)$  $A_i \ldots A_n$ ).

Dynamic memory device 101 can be connected to other components via data terminal 120 or optional terminal 116.

2

Optional terminal 116 can provide control signal 121 for address generator 112. For example, control signal 121 can be a clock signal.

In one refresh cycle, address generator 112 generates block addresses 119  $(a_1, a_i \dots a_n)$  for all blocks 113  $(A_1, a_1, \dots, a_n)$  $A_i \dots A_n$ ) of memory array 110. Block addresses  $a_1, a_i \dots$ a, can have, for example, ascending or descending values. Block addresses  $a_1, a_i \ldots a_n$  are supplied to decoder 114. Decoder 114 sends refresh signals 115 to corresponding blocks 113 on memory array 110. Upon receiving refresh signal 115 the information of all storage elements 111 of one block 113 is updated by data accessing means 118, thus each block 113 is refreshed. At the end of each refresh cycle, address generator 112 resets automatically and the cycle can start again when a clock signal is available. The clock signal can be supplied as control signal 121 via optional terminal

116. It can also be generated by address generator 112 itself. It is frequently the case with a DRAM, that data is stored in an array comprising memory cells which are arranged for example in rows. In such a case the memory cells correspond to storage elements 111, the rows to blocks 113, a counter to address generator 112, a row decoder to decoder 114, and data accessing means 118 comprises charge detection circuits for reading the information. Row addresses are generated in the counter and supplied to the row decoder. The row decoder is connected to each row via outputs 117. The signals at the outputs of the row decoder are the above mentioned refresh signals 115. When refresh signal 115 is applied to a particular row, the information of every single memory cell of that particular row is read and the capacitor of that memory cell is recharged if required, thus that row is refreshed.

For convenience of explanation and not intended to be limiting the following example is given:

In a DRAM having an array of 1024×1024 memory cells for storing 1 Mbit data, the memory cells are arranged in 1024 rows designated as  $A_1 \dots A_{1024}$ . The row decoder is connected to each row and supplies above mentioned refresh signals 115 to the rows. The counter produces increasing addresses  $a_i$  which are integer numbers from  $a_1=1$  to  $a_{1024}=$ 1024. When, for example, the address  $a_{256}=256$  is supplied to the input of the row decoder then all 1024 memory cells of row A<sub>256</sub> are refreshed one after another. The charge of each memory cell is detected by a charge detection circuit which is part of data accessing means 118. If the memory 45 cell is charged, than it is recharged. That means that all memory cells with charged capacitors (e.g., representing the bit "1") are recharged, and these with uncharged capacitors (e.g., representing the bit "0") are not recharged.

A DRAM usually also includes data accessing means 118 to read the information of each memory cell. Additional 50 addresses such as, for example, column addresses are required to access each memory cell. That additional addresses can be supplied via data terminal 120.

In dynamic memory device 101 of FIG. 1, all blocks 113 of memory array 110 are refreshed in every refresh cycle, thus consuming energy.

The invention provides an improved refresh circuit for dynamic memory devices and a method for refreshing such devices that reduces or overcomes the above mentioned <sup>60</sup> problems of prior art.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 shows a schematic diagram of a dynamic memory device as known in prior art; and

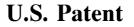

FIG. 2 shows a schematic diagram of a dynamic memory device with modified refresh circuit according to a preferred embodiment of the invention.

40

45

50

60

#### DETAILED DESCRIPTION OF THE DRAWINGS

FIG. 2 shows a schematic diagram of dynamic memory device 201 with modified refresh circuit 230 according to a preferred embodiment of the invention.

As in the prior art, dynamic memory device 201 comprises memory array 210, address generator 212 and decoder 214. Additionally, dynamic memory device 201 comprises reference register 222 or other storage means and control logic 224. Dynamic memory device 201 also comprises data terminal 220 and optional terminals 216, 226, 236.

The combination of address generator 212 and decoder 214 is referred to as signal provider 260. The combination of reference register 222 and control logic 224 is referred to as signal controller 270. Signal provider 260 and signal con- 15 troller 270 form refresh circuit 230.

As in the prior art, memory array 210 comprises a multitude of storage elements 211 and data accessing means 218. Data accessing means 218 is provided to write, read and update data which is stored in storage elements 211. Data 20 accessing means 218 is connected to storage elements 211 and to data terminal 220. Optional terminal 216 can provide control signal 221 for address generator 212. For example, control signal 221 can be a clock signal.

A physical group of storage elements 211 in memory <sup>25</sup> array 210 is referred to as block 213. Each block 213 is logically designated by  $A_1, A_i \dots A_n$ . In memory array 210, the number of blocks **213** is n. Block addresses **219**  $a_1, a_2, \ldots$  $a_n$  are logically assigned to blocks  $A_1, A_1, \dots, A_n$ . There is one address  $a_i$  for one block  $A_i$ . Outputs 217 of decoder 214 are <sup>30</sup> connected to storage elements 211 of corresponding blocks 213.

In FIG. 1 and FIG. 2 the reference numbers 101/201, 110/210, 111/211, 112/212, 113/213, 114/214, 115/215, 116/ 216, 117/217, 118/218, 119/219, 120/220, 121/221, 130/230 stand for analogous components or signals. However, their operation or function is different as a consequence of the embodiment which will be explained in detail referring to FIG. 2.

Reference register 222 is used to store a reference address  $a_r$ . In FIG. 2, reference address  $a_r$  is indicated by number 223. The reference address  $a_r$  can be provided to reference register 222 by optional terminal 226. Control logic 224 is connected at input 227 to address generator 212 and at input 229 to reference register 222. Decoder 214 is equipped with ENABLE-input 234 connected to output 225 of control logic 224. Optional link 250 can be provided between memory array 210 and reference register 222. Optional terminal 236 can be provided for feeding signals to control logic 224.

Address generator 212 continually supplies block addresses 219  $(a_1, a_i \dots a_n)$  to decoder 214.

The constant reference address  $a_r$  appears at input 229 of control logic 224. At input 227 of control logic 224 an address  $a_i$  of the changing addresses  $a_1, a_i \ldots a_n$  from 55 address generator 212 is present. Control logic 224 compares this address  $a_i$  with the reference address  $a_r$  and switches decoder 214 ON and OFF according to a logical function  $f(a_i, a_r)$  implemented in control logic 224. The logical function  $f(a_i, a_r)$  can be expressed by terms such as greater or smaller than, odd or even, modulo, etc. In that way, decoder 214 sends refresh signals 215 to memory array 210 only when it is enabled by control logic 224 at ENABLE-input 234.

be supplied to reference register 222 via optional terminal 226 or it can be stored internally. The logical function can be implemented in control logic 224, but any means for supplying the logical function  $f(a_i, a_r)$  to control logic 224 can also be used. For example, the logical function  $f(a_i, a_r)$  can be supplied to control logic 224 via optional terminal 236 or it can be supplied via optional terminal 226 or optional terminal **216** or a combination thereof, or it can be stored within dynamic memory device 201.

In the preferred embodiment for a DRAM, control logic 224 is a comparator. For example, control logic 224 enables <sup>10</sup> decoder **214** for  $a_i < a_r$  and for  $\hat{a}_i = a_r$ . It disables decoder **214** for  $a_i > a_r$ . For example, assume there are n=1024 rows from  $A_1$  to  $A_{1024}$  which have addresses from  $a_1=1$  to  $a_{1024}=1024$ , and that reference register 222 has the value of  $a_r = a_{512} = 512$ . Address generator 212 generates addresses  $a_i$  which are in this example numbers from 1 to 1024 and returns to 1. When these addresses are smaller or equal to 512 than decoder 214 is enabled and rows  $A_1$  to  $A_{512}$  are refreshed. Then address generator 212 counts further from 513 to 1024, but decoder 214 is disabled and rows  $A_{513},\!A_{514}$  . . .  $A_{1024}$  are not refreshed. In that example, refreshed rows  $A_1, A_2 \dots A_{512}$ are contiguous. This is convenient but not essential. Rows  $A_{513},\,A_{514}\,\ldots\,A_{1024}$  which are not refreshed can also be contiguous.

In another example for a DRAM, control logic 224 has a different logical function  $f(a_i, a_r)$ . For example, when  $a_r=1$ , control logic 224 can enable decoder 214 for even block addresses a, and disable decoder for odd block addresses a,. For  $a_r=0$ , control logic 224 can always enable decoder 214, independently of whether block address a, is even or odd. In that case  $a_r$  can have only one bit.

In all cases, the operation of address generator 212 with the generation of all block addresses  $a_1, a_2, \ldots, a_n$  in one cycle can be the same as in prior art. Address generator 212 and reference register 222 are independent. The number of blocks 213 in memory array 210 to be refreshed depends only on the reference address  $a_r$  of reference register 222 and of the logical function  $f(a_i, a_r)$  which commands control logic 224.

In comparison to the prior art, where all blocks 113 and therefore all storage elements 111 are refreshed, the present invention of FIG. 2 allows one to divide the total number of storage elements 211 into two sets: a first set of storage elements 211 to be refreshed, and a second set of storage elements 211 not to be refreshed. The term "set" is also applicable to blocks 213: storage elements 211 of the first set of blocks 213 are to be refreshed, and storage elements 211 of the second set of blocks 213 are not to be refreshed. In other words, refresh circuit 130 of prior art allows only full refresh of an array; and refresh circuit 230 of the present invention allows not only full but also partial refresh of an memory array of storage elements. It is also included in the present invention that reference address a, and logical function  $f(a_i, a_r)$  can be supplied from outside dynamic memory device 201.

When a system which uses dynamic memory device 201 requires full memory capacity, reference register 222 can be set to a certain value  $a_{r0}$ , preferably equal to but not excluding the lowest address  $a_1$  or the highest address  $a_n$  of address generator 212. Then, memory array 210 can store the maximum amount of data because it will be refreshed completely on each refresh cycle. The above mentioned first set contains all blocks **213** and the second set is empty.

The present invention is not limited merely to the use of The reference address  $a_r$  or information to produce it can 65 one address generator 212, reference register 222 or control logic 224. Additional units can be used and combined in order to specify blocks 213 to be refreshed more flexibly.

This is especially important if dynamic memory device **201** is a Content Addressable Memory in which the blocks to be refreshed need to be controlled by the system in which dynamic memory device **201** is used.

By optimizing refresh circuit **230** it can be guaranteed that <sup>5</sup> critical data is stored even if a reference register **222** fails. Memory array **210** is refreshed completely and failure of reference register **222** only influences the power consumption and not the security of data, thus providing fail-safe operation. 10

The reference address  $a_r$  as well as the logical function  $f(a_i, a_r)$  and therefore blocks **213** to be refreshed can be determined by software and adjusted to the requirements of the system and of each application.

In a further embodiment of the invention, reference register 222 can be set to a certain value  $a_{r fx}$ . That value can not be changed from outside dynamic memory device 201. In such a configuration, control signal 237 is provided at optional terminal 236. Depending on control signal 237 memory array 210 is refreshed fully or only partially <sup>20</sup> refreshed.

In a still further embodiment of the invention, reference register 222 is coupled by optional link 250 directly to data accessing means 218. The reference address  $a_r$  is part of the  $_{25}$  data stored in the DRAM.

Applications for the inventions can be found for a wide range of battery powered portable systems, as for example, lap top computers, portable computer games, cellular telephones, pagers, hearing aides, etc.

The above mentioned communication and other systems often operate for a significant period of time in standby mode when only a certain amount of data needs to be stored. When activated to full operation, the system requires full memory capacity available within very short time. The <sup>35</sup> present invention makes such operation possible without use of static memory.

The applications are not limited to such systems. There are many other stationary and remote systems where the power source is difficult to maintain or even impossible to replace as, for example, in solar or wind powered transmitters, remote earthquake or temperature sensors, emergency beacons, and in satellites. For example, reducing size and power consumption of an implantable medical device has an appreciable advantage for the patient, since the battery needs to be exchanged less often or not at all. With further reduction of energy consumption, dynamic memory devices can be used in applications from which they had been previously excluded.

It will be appreciated that although only one particular embodiment of the invention has been described in detail, various modifications and improvements can be made by a person skilled in the art based on the teachings herein without departing from the scope of the present invention. 55

The space which the hardware of the inventive refresh circuit requires is very small compared to the other elements. As the improved hardware is compatible with existing software, there is no need to modify software at the same time as introducing the present invention. Compared to the 60 prior art solution of combining static and dynamic devices, the use of expensive hardware such as for static memory devices can be significantly reduced or avoided, thus increasing reliability and cost saving.

I claim:

1. A dynamic memory device comprising:

(a) a plurality of storage elements;

- (b) a signal provider for sending refresh signals to said storage elements and for providing addresses of substantially all storage elements; and

- (c) a programmable signal controller coupled to said signal provider for receiving said addresses and for comparing magnitudes of said addresses to a magnitude of a reference address, said programmable signal controller for controlling said signal provider so that, during a particular refresh cycle in which addresses for substantially all storage elements are generated, only a first sub-set of storage elements with addresses in a first magnitude relation to said reference address are refreshed and a second sub-set of storage elements with addresses in a second magnitude relation to said reference address are not refreshed.

- 2. A dynamic memory device comprising:

- (a) a plurality of storage elements;

- (b) a signal provider for sending refresh signals to said storage elements; and

- (c) a programmable signal controller coupled to said signal provider for controlling said signal provider so that, during a particular refresh cycle, only a first sub-set of storage elements are refreshed and a second sub-set of storage elements are not refreshed, said signal provider having

- (i) an address generator for providing addresses for said storage elements; and

- (ii) a decoder for receiving said addresses from said address generator and, in response to a control signal received from said signal controller, sending refresh signals to said first sub-set of storage elements but not to said second sub-set of storage elements,

- said signal controller having a reference register for storing a reference address and control logic coupled to said reference register, to said address generator, and to said decoder, wherein said control logic uses said addresses generated by said address generator and said reference address to determine which storage elements are in said first sub-set and which storage elements are in said second sub-set.

3. The dynamic memory device of claim 2 wherein the reference address is supplied to said reference register by an external terminal.

4. The dynamic memory device of claim 2 wherein said control logic is controllable by a signal applied to an external terminal.

5. A method for the refresh of dynamic memory devices having a plurality of rows with storage elements, comprising <sub>50</sub> the steps of:

- a) storing a reference address;

- b) generating an address for one of said rows;

- c) relating said row address and said reference address by a logical function, thereby determining if a magnitude of said row address belongs to a first sub-set or a second sub-set of magnitudes of row addresses;

- d) sending refresh signals to said row only if said row address belongs to said first sub-set; and

e) repeating said steps b) to d) for substantially all rows.

- 6. A memory comprising:

- an array of rows;

65

- a generator which continuously generates row addresses; and

- a filter coupled between said generator and said array, said filter consecutively relating substantially all of said row addresses to a reference address and depending on a

25

comparison between said reference address and said row addresses sending refresh signals to some of said rows and not sending refresh signals to the other rows.

7. A memory comprising:

an array of rows;

- a generator which continuously generates row addresses; and

- a filter coupled between said generator and said array, said filter consecutively relating substantially all of said row addresses to a reference address and sending refresh signals to some of said rows and not sending refresh signals to the other rows said filter having

- (a) a decoder receiving said row addresses and sending refresh signals, and

- (b) a comparator receiving said reference address once <sup>15</sup> and said row addresses consecutively, said comparator enabling said decoder or disabling said decoder.

- 8. An apparatus comprising:

- a plurality of n blocks  $A_i$  (i=1 to n), each block  $A_i$  being 20 accessible by a single address  $a_i$ ;

- a generator which in a single refresh cycle provides addresses  $a_i$  from i=1 to i=n in any order;

- a register for storing a reference address; and

a comparator

receiving an address a<sub>i</sub>;

- every time said comparator has received an address  $a_i$ , comparing said address  $a_i$  with said reference address, and

- every time said comparator has compared, selectively <sup>30</sup> forwarding said address  $a_i$  to  $A_i$  so that a refresh operation is executed in some of said n blocks, but not in all blocks  $A_i$ .

9. The apparatus of claim 8 wherein said reference address is constant during a single refresh cycle.

8

10. The apparatus of claim 8 wherein said reference address is provided from an external terminal.

- **11**. A dynamic memory comprising:

- a plurality of n rows A<sub>i</sub> (i=1 to i=n) each having storage cells;

- a generator which cyclically generates addresses a<sub>i</sub> for i=1 to i=n;

- a decoder receiving one address  $a_i$  at a time, said decoder being either enabled or disabled, said decoder when enabled sending a refresh signal to said storage cells of row  $A_i$  which is identified by said address  $a_i$ ; and

- a control logic cyclically receiving addresses  $a_i$ , and enabling or disabling said decoder depending on a logical relation between and a reference address  $a_r$ .

- **12**. A dynamic memory comprising:

- a plurality of n rows A<sub>i</sub> (i=1 to i=n) each having storage cells;

- a generator which cyclically generates addresses a<sub>i</sub> for i=1 to i=n;

- a decoder receiving one address a<sub>i</sub> at a time, said decoder being either enabled or disabled, said decoder when enabled sending a refresh signal to said storage cells of row A<sub>i</sub> which is identified by said address a<sub>i</sub>; and

- a control logic cyclically receiving addresses  $a_i$  and enabling or disabling said decoder depending on a logical relation between  $a_i$  and a reference address  $a_i$ , said control logic enabling the decoder for  $a_i < a_r$  and  $a_i = a_r$  and disabling said decoder for  $a_i > a_r$ , wherein r is a predetermined integer between from 0 to n.

**13**. The dynamic memory of claim **11** which receives said reference address from an external terminal.

\* \* \* \* \*

# EXHIBIT B

## United States Patent [19]

#### Allen et al.

#### [54] COMPLIMENTARY DOUBLE PUMPING VOLTAGE BOOST CONVERTER

- [75] Inventors: Steven Peter Allen, Mesa; Ahmad H. Atriss, Chandler; Gerald Lee Walcott, Mesa; Walter C. Seelbach, Fountain Hills, all of Ariz.

- [73] Assignee: Motorola, Inc., Schaumburg, Ill.

- [21] Appl. No.: 09/130,343

- [22] Filed: Aug. 13, 1998

- [51] Int. Cl.<sup>7</sup> ..... H03L 5/00

- [52] U.S. Cl. ...... 327/306; 327/536; 327/537;

- 327/589

[58] Field of Search

327/534, 536,

- 327/530, 537, 390, 306, 331, 589; 365/185.23

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 5,644,534 | 7/1997 | Soejima 365/185.23 |

|-----------|--------|--------------------|

| 5,889,428 | 3/1999 | Young 327/536      |

## [11] Patent Number: 6,127,875

### [45] **Date of Patent:** Oct. 3, 2000

5,917,367 6/1999 Woo ...... 327/537

Primary Examiner-Tuan T. Lam

Assistant Examiner-Hiep Nguyen

Attorney, Agent, or Firm—Lanny L. Parker; A. Kate Huffman

#### [57] ABSTRACT

A voltage boosting circuit which derives an output voltage than is substantially twice the magnitude of a supply voltage applied thereto. The voltage boosting circuit consists of complementary acting boost circuits each having a pair of switches (42A, 52A; 42B, 52B) connected between an input of the voltage boosting circuit, at which is applied the supply voltage, and an output at which the output voltage is produced. Boost capacitors (48A, 48B) are connected between the respective switches of the complementary boost circuits and the switches of the these circuits are opened and closed out of phase with respect to each other in response to clocking signals being applied thereto such that a boosted output voltage is produced during each half cycle of the clocking signals.

#### 3 Claims, 2 Drawing Sheets

U.S. Patent

Sheet 1 of 2

- PRIOR ART -

## Oct. 3, 2000

Sheet 2 of 2

#### COMPLIMENTARY DOUBLE PUMPING **VOLTAGE BOOST CONVERTER**

#### BACKGROUND OF THE INVENTION

The present invention relates to voltage boosting convert- 5 ers and, more particularly to a double pumping voltage boosting circuit for providing an output voltage greater than a supplied input voltage and which is suited to be manufactured in integrated circuit form.

The evolution of integrated circuit technology has pro- 10 vided for ever smaller device geometry's with lower operating supply voltages. The lower supply voltage has resulted in advantages and disadvantages with the primary advantage being a significant reduction in power consumption. A significant disadvantage is the inability of some of the more 15 complex functions to operate at the lower supply voltage. To facilitate these functions, a localized voltage boosting circuit is needed to supply an increased operating voltage. The voltage boosting circuit should be efficient in terms of power consumption, component count and die area while deliver- 20 ing an increased supply voltage with minimal amounts of ripple or distortion.

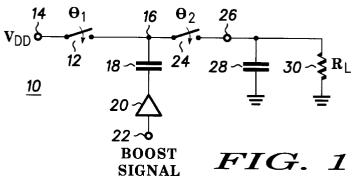

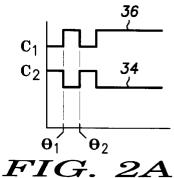

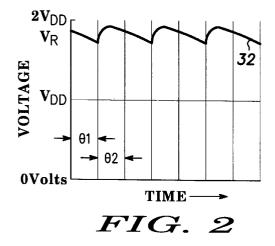

A basic voltage boosting circuit 10, that is well understood in the art, is illustrated in FIGS. 1, 2, and 2A. Circuit 10 uses two switches 12 and 24 for controlling the current 25 flow and two capacitors 18 and 28 for boosting and storing an output voltage applied across a load resistor **30** which is derived from a supply voltage  $V_{DD}$  supplied at an input 14. The circuit operation begins by first referencing the boosting capacitor 18 to the supply voltage and ground reference 30 potential by having switch 12 closed during the first half cycle,  $\eta_1$ , in response to a pair of non-overlapping clock signals C1 and C2, which are 180 degrees out of phase with respect to one another, while the output of buffer 20 is in a low voltage level state due to a boost signal applied thereto. 35 This connects the top of capacitor 18 to  $V_{DD}$  while the bottom is at ground reference potential. In the second half cycle,  $\Theta_2$ , switch 12 opens and buffer driver output drives from a low voltage level state to a high voltage level state boosting the potential at the top of capacitor 18 to substan-40 tially twice the supply voltage  $V_{DD}$ . Simultaneously, switch 24 closes so that the boosted charge on capacitor 18 can be distributed between itself and storing load capacitor 28. The resulting output voltage  $V_R$ , depicted in FIG. 2, shows the boosted voltage on capacitor 28 decaying as current is 45 boosted to nearly  $2V_{DD}$  as illustrated in FIG. 4, to drive into delivered in the load  $R_L$ , during the first half of the clock cycle,  $\Theta_1$ . During the second half of the clock cycle,  $\Theta_2$ , the output voltage first builds toward  $2V_{DD}$ , due to the boosted charge on capacitor 18 being redistributed across capacitors 18 and 28, and then decays as current is delivered to the load. 50 The resulting output voltage contains a significant amount of distortion due to the discrete charge and decay times. Furthermore, it typically takes 1600 pF of capacitance for both capacitors to deliver 1.2 ma of current while boosting the voltage from 0.9 volts to 1.4 volts, at a 10 MHz clock 55 ering the boosted voltage into load 58, capacitive device 48A rate.

Hence, a need exists for an improved voltage boosting circuit suitable for fabrication in integrated circuit form for boosting a supply voltage while requiring less capacitance and output voltage distortion than known prior art voltage 60 boosting circuits.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a schematic diagram of a prior art voltage boosting circuit;

FIG. 2 shows the output voltage produced by the prior art circuit of FIG. 1;

2

FIG. 2A shows the clocking signals useful for explaining the operation of the present invention;

FIG. 3 is a schematic diagram of one embodiment of the present invention;

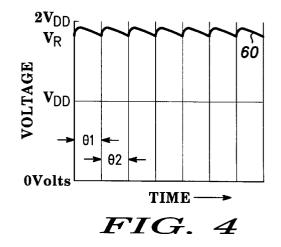

FIG. 4 shows the output voltage produced by the embodiment of the present invention;

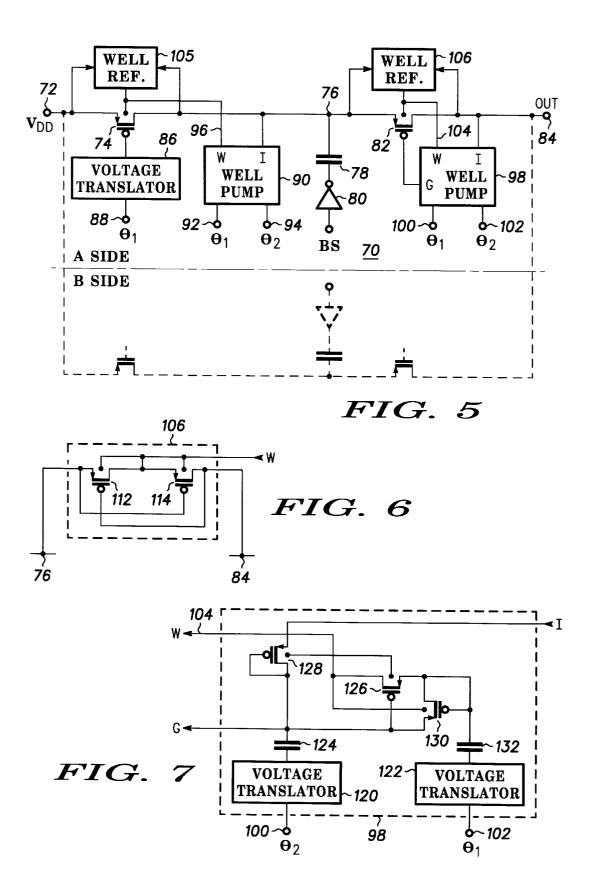

FIG. 5 is a partial block and schematic diagram of the voltage boosting circuit of the present invention shown in FIG. 3;

FIG. 6 is a schematic diagram of the well reference circuit shown in FIG. 5; and

FIG. 7 is a schematic diagram illustrating a well pump circuit disclosed in FIG. 5.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

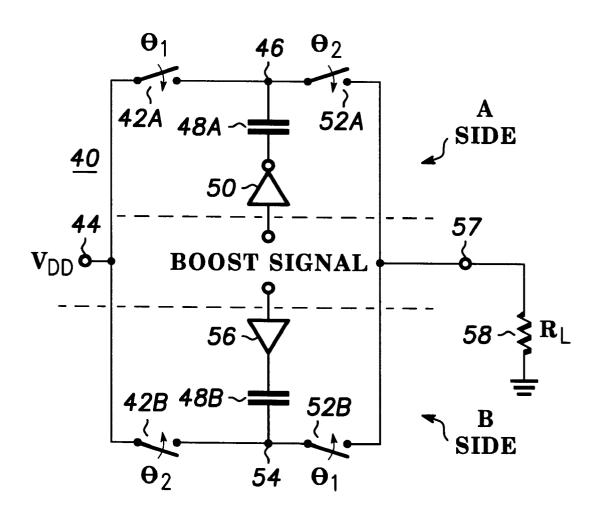

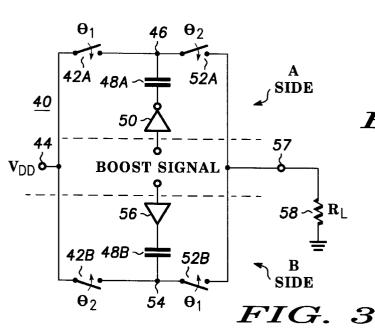

Turning now to FIG. 3 there is shown double pumping voltage boosting converter 40 of the preferred embodiment of the present invention. Voltage boosting circuit 40 comprises an A side voltage boost circuit portion similar to the prior art circuit of FIG. 1 and a complementary (B side) voltage boost circuit portion. Thus, the complementary pumping architecture of FIG. 3 includes first switches 42A and 42B connecting a supply voltage  $V_{DD}$ , applied to terminal 44, to respective terminals 46 and 54 when the switches are closed and disconnecting terminal 44 from terminals 46 and 54 when opened. The A side circuit portion further includes capacitive device 48A connected between terminal 46 and the output of inverting buffer driver 50. Likewise, B side circuit portion includes capacitive device 48B coupled between terminal 54 and non-inverting buffer driver 56. Terminals 46 and 54 are coupled respectively via a pair of switches 52A and 52B to output 57 of voltage boosting circuit 40 which is, in turn, connected to load device 58, shown here as a resistor  $R_L$ . A voltage boost signal is applied to the inputs of buffer drivers 50 and 56.

Thus, in operation, during the first half cycle,  $\Theta_1$ , of the clocking signals 34 and 36, switches 42A and 52B are closed while switches 42B and 52A are opened. If it is assumed that the capacitive device 48B has been charged to  $V_{DD}$  during a previous half cycle, and at the same time switch 52B is closed, the boost signal is in a high level state, as previously described, the voltage across capacitive device 48B will be load 58. As current flows in load 58 the charge across capacitive device 56 begins to decrease but to a much less degree than for prior art circuit 10. Simultaneously, the boost signal applied to inverting buffer 50 is driving its output to a low level state, is referencing capacitive device 48A between  $V_{DD}$  and ground potential as switch 42A is closed while terminals 46 and 54 are disconnected from output terminal 57 and input terminal 44 respectively as the switches are open. Thus, as capacitive device 48B is delivis being charged to  $\mathrm{V}_{DD}$  . Conversely, during the second half cycle,  $\Theta_2$ , switches 42B and 52A are closed while switches 42A and 52B are opened. Boost signal also changes states from a high level to a low level. Hence, the A side of voltage boosting circuit 40 drives load 58 with a voltage nearly equal to  $2V_{DD}$  as the voltage across capacitive device 48A is boosted to the higher voltage level while  $V_{DD}$  is applied across capacitive device 48B. Thus, during initiation of both half cycles  $\Theta_1$  and  $\Theta_2$ , as illustrated in FIG. 4, the voltage  $_{65}$  drive into load 58 is raised to nearly  $2V_{DD}$ .

The output voltage  $V_R$ , wave form 60, is shown to have much less distortion as boost capacitors 48A and 48B deliver

15

charge into load 58 during both phases of the clocking pulses which reducing the discharge time that  $V_R$  decreases which is a significant advantage over the prior art. Additionally, the need for an added load capacitance, capacitor 28, is eliminated by voltage boosting circuit 40 since either capacitive device 48A or capacitive device 48B is driving load 58 at all times. Hence, not only is the need for one capacitive device eliminated by the present invention but the individual capacitance value of the two driving capacitive devices thereof are significantly reduced. Therefore, the die area needed for fabricating voltage boosting circuit 40 in integrated circuit form compared to circuit 10 is significantly reduced.

In one example, a voltage boosting circuit of the present architecture has been found to use 400 pF of capacitance for capacitive devices **48**A and **48**B to deliver 1.2 ma of current to a load while boosting the voltage applied thereto from 0.9 volts to 1.4 volts, at a 10 Mhz clock rate while reducing the output voltage distortion when compared to the voltage boost circuit of the prior art. The prior art boost circuit required 3200 pF of capacitance to achieve the same performance. This represents a significant savings in die area.

Turning now to the remaining figures, the voltage boosting circuit architecture of the present invention is shown in more detail. For brevity, FIG. 5 illustrates only the A side portion 70 of the voltage boosting circuit 40 described in 25 FIG. 3, it being understood that the B side portion is identical thereto.

Switches 42A, 52A (as well as 42B and 52B) are illustrated as being realized by PMOS transistors. PMOS transistor 74, switch 42A, is shown as having its source elec- 30 trode coupled to input 72 to which is applied supply voltage while its drain is coupled to terminal 76 at one side of capacitor 78. The other side of capacitor 78 is coupled to the output of inverting buffer driver 80 the latter of which has an input to which the boost signal is applied. Switch 52A is 35 illustrated, an output of voltage translator 120 is coupled shown as being realized by PMOS transistor 82 having its source electrode coupled to terminal 76 and its drain electrode coupled to output 84. Output 84 would be connected a to load which, not shown, would be similar to load 58 of FIG. 3. A voltage translator 86 which has an input 88 for  $_{40}$ receiving the clock pulse C1 provides a translated voltage, as is understood to those skilled in the art, to drive the gate electrode of transistor 74 such that the gate potential is of sufficient magnitude to insure that the transistor remains off whenever its gate is driven high. Similarly, a voltage trans- 45 drain is connected to the floating well of switch transistor 82 lator is provided, as will be discussed, for driving the gate electrode of transistor 82 in a complementary phase with respect to transistor 74. All translators receive their supply voltage from the converter output, node 84.